|

摘要:CPU设计不再是大团队的特权,RISC-V官网列出的RISC-V CPU内核已经超过一百多个。RISC-V解放了ISA,现在是时候解放CPU和其他组件,把专利留给更大的进步。

在官网riscv.org/exchange/上,现在列出的RISC-V CPU内核超过一百多个。如果你需要一个RISC-V CPU内核,就可能从中找到一个适合的需求…当然,你需要评估这一百多个CPU内核,以准确配置您的需求,并在几秒钟内免费构建它!

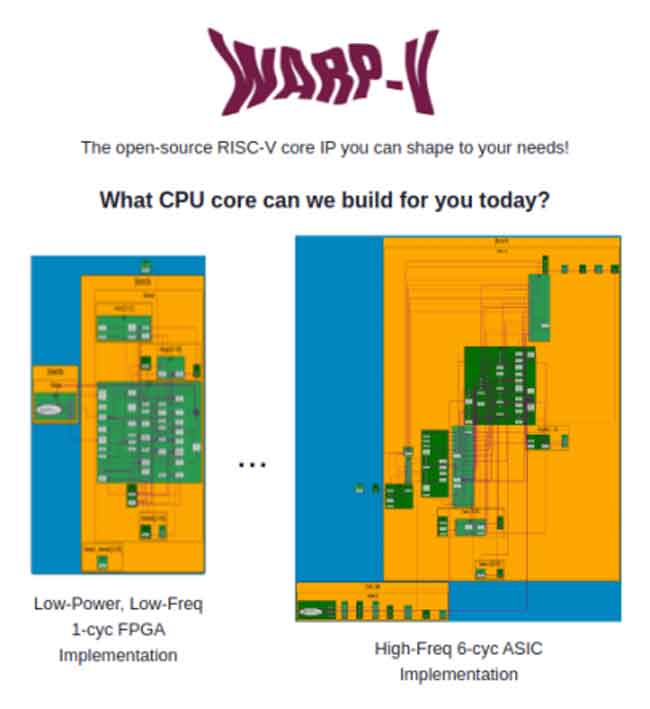

WARP-V是最灵活的RISC-V CPU内核,最近,印第安纳大学的学生亚当・拉兹曼(Adam Ratzman)为WARP-V创建了一个在线配置器。如果你需要一个中低端CPU内核,请查看亚当在warp-v.org.warp・v.org WARP-V内核的工作。

我职业生涯的大部分时间都在设计高端CPU,这比我们上面谈的更复杂。在单核性能竞赛中,CPU经历了复杂性不断增加的疯狂循环,随后是简化需求。

技术趋势对我们开了一个有趣的玩笑。在90年代,由于摩尔定律给了更多的硅来玩,我们狼吞虎咽地实现了下一个wiz-bang投机伎俩,以获得1%的单流性能优势。但是现在这样的把戏在很多方面都对我们不利:

(1)更大的内核,意味着更长的导线和RC延迟,在现代工艺中,这主导了周期时间并降低了性能。

(2)更大的功率,我们必须以此来换取性能。

(3)会耗尽空间,这意味着内核数量减少,从而降低性能。

(4)增加了设计工作量,这意味着需要更长时间来优化下一个流程节点,这会影响性能。

这一切都是在说,CPU设计不再需要500人的设计团队。我在2018年用了一周半的时间开发了最初的WARP-V内核。它不包含我在职业生涯中学习和开发的任何高级CPU微体系结构技术。这可能正是你想要的。另一方面,WARP-V的独特之处在于它的灵活性。您将能够相对快速地根据自己的需求对其进行优化,现在,这就是我们获得性能的方式。

WARP-V灵活性的秘密,也是我的初创公司Redwood EDA的重点,是事务级Verilog (TL-Verilog)。TL-Verilog使WARP-V能够从相同的源代码中提供单周期CPU、七周期CPU或介于两者之间的任何能力。它提供了使用相同的单页代码将WARP-V的任何配置连接到第三方RISC-V形式检查器的能力。它有助于将ISA从微体系结构中分离出来,因此除了RISC-V之外,WARP-V还可以支持MIPS和其他ISA。你无法从RTL获得这种灵活性,而这种灵活性是成功芯片的关键。

WARP-V可能不是今天每个人的最佳选择。到目前为止,它一直是一个小规模的努力,目前只是CPU核心,没有与外围设备捆绑在一起。但它应该很好地服务于社区的很大一部分,并且显示了一种不需要一百个不同的独立核心就能使CPU平民化的方法。

RISC-V解放了ISA。现在是时候解放CPU和其他组件,把专利留给更大的进步。

编译:镨元素

英文:https://semiwiki.com/ip/risc-v/300408-a-free-risc-v-cpu-core-builder-democratizing-cpus/

|