下一代平台对带宽、灵活性和功能的要求越来越高,同时还有降低功耗指标,减小引脚布局的要求。本白皮书介绍下一代平台的系统需求,解释为什么传统的解决方案无法有效的满足这些需求。文章还介绍了Stratix 10 FPGA和SoC所采用的Altera异构3D系统级封装(SiP)技术。这一技术提高了带宽,降低了功耗,减小了外形尺寸,增强了功能和灵活性,支持下一代平台的实现。Stratix 10 FGPA和SoC在所有密度上都采用了基于3D SiP的收发器。本文介绍这一下一代收发器解决方案的可扩展性、灵活性和产品及时面市优势。此外,还仿真了SiP技术的物理结构,将其与其他选择进行了对比,解释了这一技术怎样满足下一代平台的特殊要求。

1. 下一代系统挑战

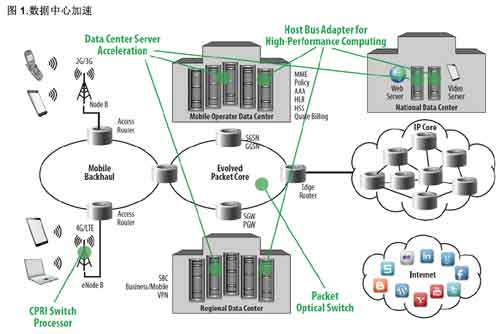

数据中心、物联网(IoT)、400G至太比特网络、光传送、5G无线、8K视频等新应用层出不穷,促使下一代平台迅速发展,以满足新出现的系统要求。互联和处理能力的不断扩展显著影响了半导体领域,从所采用的元器件类型直至更高效的系统和相关服务。对这一新兴领域的详细研究揭示了一些令人关注的发展趋势。

例如,下一代数据中心工作负载对计算能力、灵活性和功效的要求越来越高;这已经超出了目前通用服务器的能力范围。此外,数据中心基础设施必须是可视化的,以商用服务器承载服务的形式交付,从而降低复杂度,在商业上更灵活,而且可扩展。但是,服务器性能提高会很慢,这主要是由于功耗限制。针对某些工作负载来设计数据中心解决方案能够提高效率,但是严重限制了解决方案的一致性和灵活性。由于数据中心服务发展非常快,需要硬件应能够适应其发展,因此,灵活性非常重要。结果,下一代数据中心平台面临的挑战是同时提供性能更好(加速)、功效更高、更灵活的解决方案。

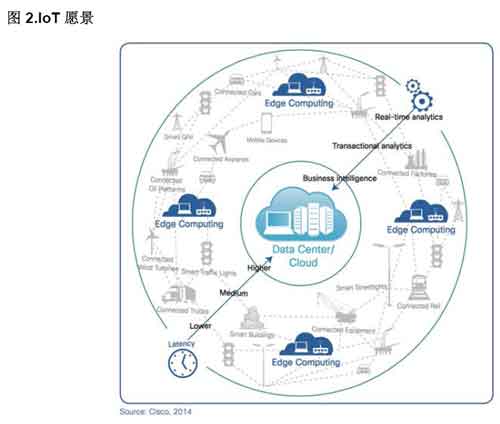

IoT反映了相似的难题。IoT增长迅速,在不久的将来会出现数十亿个“智慧物体”。这些智慧物体相互连接和通信,或者通过云和数据中心进行连接和通信。基础设施必须能够确定需要处理哪些数据,哪些数据要丢弃,这些都要实时完成。因此,IoT需要的是从数据中心直至边沿连接可靠、灵活、高效的宽带基础设施。这一需求给服务提供商、数据中心、云计算和存储系统带来了难题,互联网很难满足如此高的要求。

下一代平台反映了一种公共的底层需求:要求以更低的功耗指标和引脚布局,提高带宽和功能。简言之,用于构建这些下一代平台的器件必须能完成更多功能、更快、占用更少的印刷电路板(PCB),能耗更低,这些都必须同时实现。这种挑战就需要半导体生态系统提供创新的解决方案。

因此,设计下一代平台的系统规划人员必须要尝试满足以下需求:

■ 带宽更大

■ 功耗更低

■ 更小的引脚布局或者外形封装

■ 更多的功能

■ 更加灵活

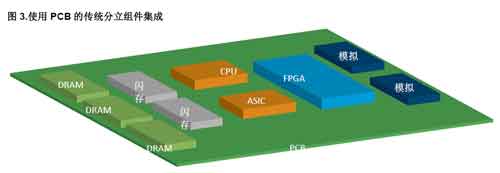

历史上,系统规划人员负责满足这些要求,他们会在标准PCB上安装更多的分立组件,尝试提供更多的功能,提高性能,同时保持在功耗预算范围内。图3描述了一个传统的解决方案,多个分立组件(FPGA、存储器、CPU等)被装配到一块标准PCB上。

这种传统的集成方法竭尽全力来满足下一代需求,已经接近其逻辑上限。一些关键的挑战包括;

■ 芯片至芯片带宽受到底层PCB最大互联密度的限制。

■ 由于需要驱动组件之间的长PCB走线,因此,系统功耗非常大。

■ 由于要实现系统功能需要大量的分立组件,因此外形封装非常大。

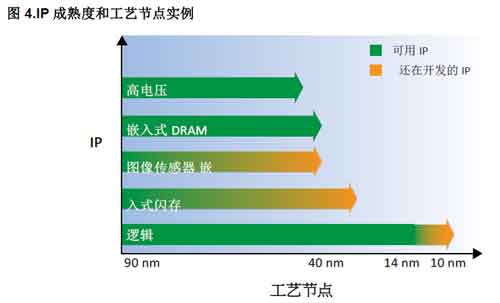

系统规划人员希望某些组件能够实现单片集成以解决这些问题。但是,这种集成直接带来了另一难题:IP是否成熟。图4显示了这一难解的问题。不同的工艺节点有成熟度不同的IP模块,在不同的时间进行扩展。因此,不可能同时集成所有必须的IP模块或者功能。例如,如果供应商采用14nm技术开发逻辑管芯,希望在片内集成DRAM,那么唯一的选择是使用40nm或者更老的技术来开发DRAM。这种局限给单片管芯解决方案的发展制造了障碍。

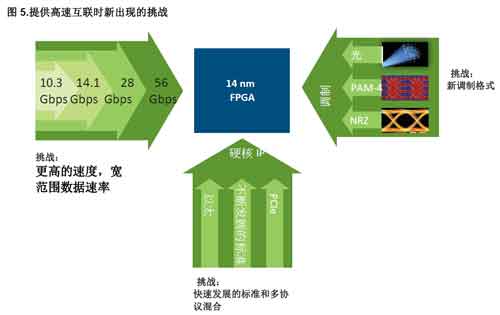

另一关键挑战是器件之间需要高速互联。Altera等FPGA供应商通过前沿的收发器技术一直在积极解决这些问题。Alter业界领先的收发器技术目前支持的数据速率超过了28Gbps。Stratix 10 FPGA和SoC等下一代器件发挥这种领先优势,数据速率计划支持到56Gbps。正如图5所示,随着高端数据速率调制方法的发展,PAM-4等新方法将得到更多的应用。而且,器件需要更多的嵌入式硬核协议IP以满足客户需求,但是,很多这些协议标准还在发展之中。因此,迫切需要一种创新的解决方案,迅速集成新出现的技术和IP模块。

下一代系统带来的挑战已经开始影响到解决方案的定义。传统的解决方案无法满足未来的需求:更大的带宽、更低的功耗、更小的外形尺寸,增强功能和灵活性。挑战是开发一种创新的、可商用、可扩展的解决方案,从而满足这些需求。

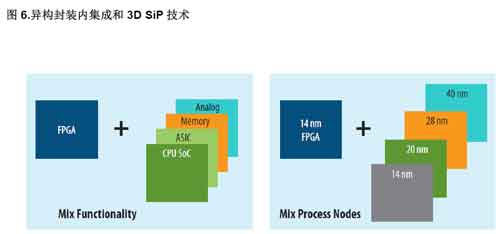

2. 使用Altera的异构3D SiP技术实现封装内集成

在Stratix 10 FPGA和SOC中,Altera推出了异构3D系统级封装(SiP)技术。这一独特的解决方案解决了所有这些挑战:更大的带宽、更低的功耗、更小的外形封装,增强功能和灵活性。它还实现了封装内集成,不但可以扩展,而且很容易直接进行制造。这一解决方案在合适的工艺节点上很好的结合了各种功能,在一个封装中为客户提供所需的系统功能。异构3D SiP技术支持多种组件的封装内集成,例如,模拟、存储器、ASIC、CPU,等等。它还在同一个封装中集成了来自不同工艺节点的收发器管芯或者收发器块。下面章节介绍了3D SiP技术与Intel的嵌入式多管芯互联桥接(EMIB)技术,封装单管芯内核架构和收发器块形成完整的解决方案。

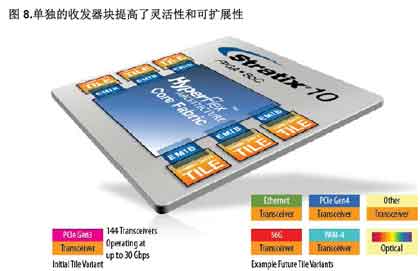

(1)基于3D SiP的收发器块:提高了可扩展能力和灵活性

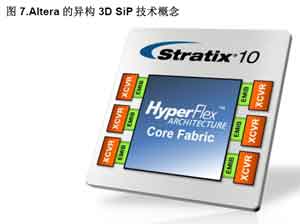

异构3D SiP技术把收发器块或者管芯从内核架构管芯中分离出来:收发器是分开的,位于内核架构管芯旁边。因此,收发器和内核架构管芯没有必要采用相同的工艺节点制造。图 7显示了这种集成概念。

异构3D SiP技术支持Altera混合多种组件以满足系统需求,比前一代更高效、迅速的提供鲁棒的解决方案。Stratix 10器件将利用成熟可靠的收发器IP,大幅度减少验证和开发时间,极大的缩短了客户的产品面市时间。展望未来,3D SiP技术提供了可扩展解决方案,能够采用PAM-4等新调制方法支持56Gbps收发器。相似的,单独的收发器块也支持定制嵌入式IP。例如,最初的Stratix 10收发器块包括一个PCIe Gen3 x16硬核IP模块。未来的版本很有可能支持各种硬核IP模组,例如PCIe Gen4、多端口以太网、光,等等,如图8所示。

这一技术之所以能够使得异构3D SiP器件得以广泛应用是因为采用了Intel获得专利、目前最先进的嵌入式多管芯互联桥接(EMIB)技术。Intel设计的EMIB面向需要高级封装和测试功能的解决方案。作为重要的14nm Intel代工线客户,Altera使用了这一最新技术。EMIB技术提供了简单的集成流程,在同一封装异构管芯之间实现了超高密度互联。这些片内封装功能对于其他可选封装内集成解决方案而言要么实现起来太复杂,要么成本过高而无法实现。如图 7所示,EMIB将收发器管芯连接至单片FPGA架构。接下来,本文将深入介绍EMIB技术,该技术相对于其他可选集成解决方案巨大的优势所在。

(2)EMIB的优势

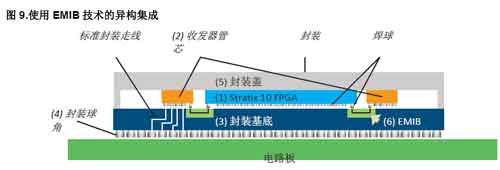

EMIB技术提供更简单的制造流程,性能更好,增强了信号完整性,降低了复杂度。图9显示了物理封装结构。该结构异构集成了FPGA内核管芯(1)和两个收发器管芯(2)。

(非FPGA管芯可以是收发器管芯、存储器管芯、CPU管芯,或者任何其他功能。)三个管芯位于标准倒装焊球栅阵列(FCBGA)封装基底上(3),基底连接至底层PCB。管芯和封装球角之间的布线使用了标准 FCBGA布线(4)。这一装配采用了标准封装盖进行封装(5),形成单封装解决方案。封装基底利用了几个嵌入式 EMIB连接(6)。EMIB使用超高密度互联连接管芯,实现了异构封装内集成。

■ 更智慧的创新封装内集成

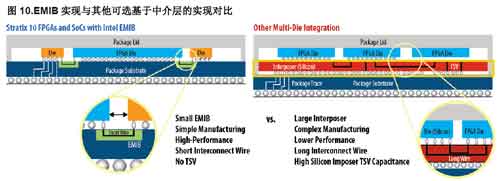

如图10所示,EMIB是嵌入在底层封装基底上的小片硅片,提供管芯间的超高密度互联。重要的是,EMIB物理尺寸并没有限制能够集成的管芯数量。作为对比,其他可选实现方法使用了大片硅片中介层,位于封装基底顶部,跨过了要集成的整个管芯。

中介层使用了全体量掩膜板,成本上难以承受,也容易出现翘曲弯曲等问题。其他可选解决方案还需要大量的微焊球,使用微过孔,这会增加生产的复杂性并影响总产量。而且,使用中介层能够集成的管芯数量受限于掩膜板大小,这影响了可扩展性。

■ 性能更好

Altera基于3D SiP的产品采用了EMIB的异构封装内集成功能,性能非常高。如图10所示,EMIB支持把要集成的管芯I/O或者焊球尽可能靠近管芯边沿放置,这是因为需要的I/O或者焊球数量很少。这一方法保证了管芯之间的物理连接非常精确,使用了短互联走线。短走线也就意味着显著减小了由走线带给驱动缓冲的负载,从而提高了性能。作为对比,其他可选解决方案使用较大的底层中介层重新连接逻辑架构。

这种同构集成方法涉及到连接大量的I/O或者焊球,将其从管芯边沿连接至中心。这种布局导致很长的互联走线,驱动缓冲会有较大的负载。最终结果是性能不高。

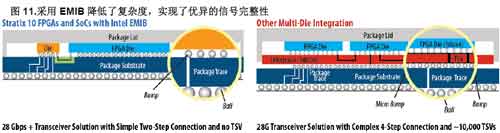

■ 降低复杂度,实现了优异的信号和电源完整性

基于EMIB的流程显著降低了制造复杂度。如图11所示,EMIB解决方案为用户I/O、电源和收发器信号提供简单的两步连接:焊球至标准封装走线,至封装球角。

标准封装布线在FCBGA封装中应用非常广泛。这种简单的连接降低了制造复杂度,实现了优异的信号和电源完整性。插入损耗交叉串扰比(ICR)和电源抑制比(PSRR)等关键参数与单片设计相当。

相反,其他可选解决方案为需要连接至封装球角的信号提供四步连接:焊球至直通硅孔(TSV),至焊球,至封装走线,至封装球角。这种连接要求为每一用户信号提供TSV,显著增加了制造流程的复杂度。(EMIB流程不使用任何TSV。)TSV是导致产量下降的主要因素,会影响商用性。而其他可选解决方案使用了大量的TSV(~10,000)。这种复杂的四步连接导致高速信号的信号完整性很差,电源分配网络的IR下降。TSV还增大了串联阻抗和电容,使得收发器模块高速设计更加复杂,难以处理。中介层布线的交叉串扰以及TSV之间的耦合会影响ICR规范;通过TSV的信号电源轨耦合会影响PSRR规范。

异构3D SiP集成是满足下一代收发器、外设、存储器等对可扩展和灵活性需求的理想解决方案,其单片FPGA架构对于满足下一代平台需求也非常关键。以下章节将详细介绍使用单片架构相对于中介层堆叠内核架构解决方案的优点。

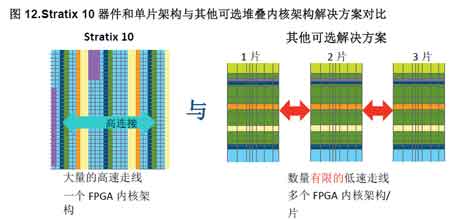

(3)单片内核架构:提高性能和利用率

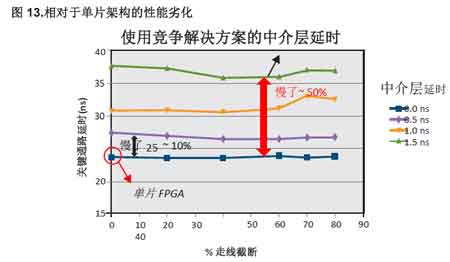

单片FPGA内核架构是提高性能和利用率的关键因素,能够以尽可能高的速率处理数据,不会出现布线拥塞、逻辑利用率瓶颈,也不会劣化性能。采用14nm三栅极技术以及新的HyperFlex内核体系结构,FPGA架构的性能比前一代平均提高了2倍。图12将Stratix 10 FPGA等具有单片架构的器件与竞争产品进行了对比,这些竞争产品的内核架构分布在多片管芯单元中,使用基于中介层的技术重新将其连接起来。

3. 结论

下一代平台迫切需要创新的解决方案,要求性能更好,功耗更低,外形封装更小。数据中心的爆炸式增长以及IoT技术的广泛应用都是关键推动因素。此外,太比特网络、光传送、8K视频和5G无线领域也发展非常迅速,促使半导体辅助支持系统寻求创新的解决方案。

Stratix 10 FPGA和SoC所实现的产品大幅度提高了带宽,降低了功耗,减小了外形封装,增强了功能和灵活性,支持多种下一代平台的实现。Stratix 10 FPGA和SoC引入了异构3D SiP技术,能够将模拟、存储器、ASIC、CPU等系统关键组件高效的进行封装内集成。这一技术采用了Intel成熟可靠的封装技术以及获得专利的 EMIB技术。

与其他可选多管芯集成解决方案相比,EMIB技术提供更简单的制造流程,性能更好,增强了信号完整性,降低了复杂度。异构3D SiP技术提高了可扩展能力,降低了风险,缩短了产品面市时间,满足了多种应用的需求。此外,Stratix 10 FPGA和SoC结合Intel的 14nm三栅极工艺技术以及HyperFlex新内核体系结构,性能平均比前一代提高了2倍。Stratix 10 FPGA和 SoC的工艺技术(14nm三栅极)、单片内核架构(采用了先进的 HyperFlex内核体系结构)以及目前最先进的封装集成(3D SiP)相结合,将给下一代平台带来革命性的变化。

作者简介

Manish Deo,Altera公司产品市场高级经理。

参考文献

■ Intel开发人员论坛2014 “采用Intel定制代工线,站在摩尔定律最前沿”,SPCS011,Sunit Rikhi。

■ 了解更多关于EMIB:http://www.intel.com/content/www/us/en/foundry/emib.html

■ 微软白皮书:加速大规模数据中心服务的可重新配置架构, Andrew Putnam, Adrian M. Caulfield, Eric S. Chung, Derek Chiou, Kypros Constantinides, John Demme, Hadi Esmaeilzadeh, Jeremy Fowers, Gopi Prashanth Gopal, Jan Gray, Michael Haselman, Scott Hauck, Stephen Heil, Amir Hormati, Joo-Young Kim, Sitaram Lanka, James Larus, Eric Peterson, Simon Pope, Aaron Smith, Jason Thong, Phillip Yi Xiao, Doug Burger.

■ 思科白皮书:实现IoT的价值:怎样从互联物体发展到深入获取,在边沿进行分析从而获得优势,Andy Noronha, Robert Moriarty, Kathy O’Connell, Nicola Villa.